Intel:还没见过先进封装就别急着评论摩尔定律

合久必分,分久必合。这不仅是天下大势,在计算机领域,甚至是在方寸之间的芯片之上,这个道理同样适用。为此,我们还专门发明了一个新的概念来形容这一现象——算力的多元化!

AI、大数据分析等应用类型的出现让数据中心对算力的需求出现了大幅增长。但另一方面,由于半导体工艺的限制,单纯靠CPU已经不能满足这些需求。因此,CPU之外的异构加速卡也成了当今很多系统的标配。

甚至,对于CPU本身来说,由于芯片规模越来越大、架构越来越复杂,其制造难度和设计成本也在迅速攀升。而这也在很大程度上限制了CPU的发展速度。

面对芯片领域越来越大的需求和制造过程越来越多的掣肘,人们在推进CPU制程和架构进化的同时也将目光瞄准了芯片本身的设计思路:

既然不能阻止算力多元化的大趋势,又不能无限制的在计算机内增加计算卡,那倒不如将这种多元化限制在封装内部。这样既能保证计算机架构的相对统一,也能在很大程度上降低芯片和系统的成本及设计制造难度。

于是,Chiplets理念应运而生。

所谓Chiplets,就是指将传统的大芯片打散成多个更容易设计和制造的小芯片并封装在一起,从而在实现更多功能、更好性能的同时降低成本。

Chiplets思路下的Intel封装进化

CPU——Central Processing Unit。

在过去,这个单数的Unit即可以指代一个封装(Package),也可以引申为一枚芯片(Die)。因为,受限于封装技术,我们极少能看到一个Package之内包含多个Die的情况。

但在Chiplets理念的影响下,CPU在Package层面仍旧是“单数”,但在Package内部的Die层面,这个Central Processing Unit的后面就很可能要加上一个“s”了。

作为半导体行业中的扛鼎力量,Intel也在经历一轮“以数据为中心”的转型,并为此构建了六大能力。而在这个从半导体到系统再到的生态的六大能力之中,Intel把制程和封装放在了最内层。言外之意很明确——制程和封装技术是Intel的立身之本。

回到Chiplets话题,这种CPU从单Die到多Die、从Unit到Units的进化之路也正是在封装技术的进步之下才得以实现的。

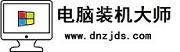

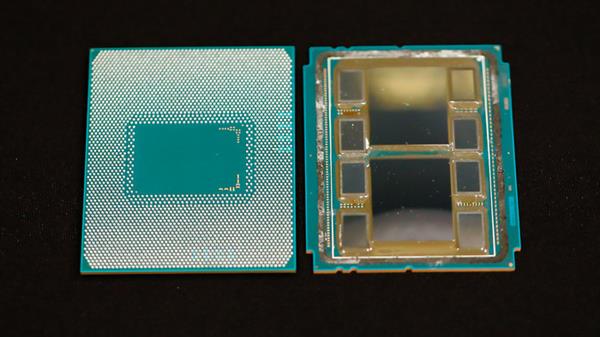

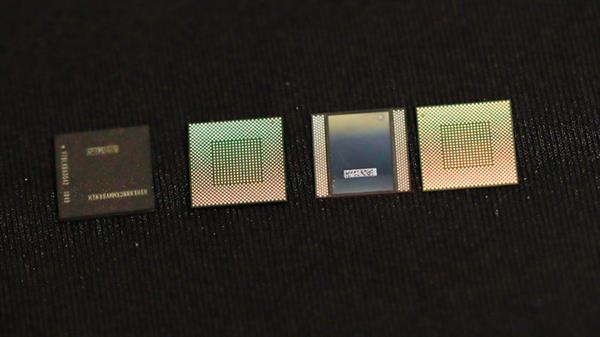

左边是Intel的CPU,中间是AMD的GPU,右边是HBM

早在2017年,就有消息传出,Intel要将自家的处理器与AMD的GPU以及HBM高速显存封装成一个芯片,以满足高性能轻薄笔记本厂商的需求。两年过去,Intel不仅拿出了这样的产品,更通过封装技术的进化打开了用户和市场在芯片封装层面的想象力大门。

9月4日,Intel在上海展示了自己最新的封装技术:可以将Die纵向堆叠在一起的3D Foveros、可以将Die在封装内水平互联的EMIB技术以及他们的结合体Co-EMIB。

对于这三种技术的原理和意义,读者老爷们可以移步《把芯片当成乐高?英特尔新思维背后的技术进步》。里面不仅有图文,更有这些技术原理的动画视频,浅显易懂、老少皆宜;这里就不再赘述。

用乐高的方式打开全新的芯片世界

乐高相对于传统积木的最大区别在于,乐高的每一个小块上都有许多圆柱形的突起,这些突起能够让无数小组件融合成为一个连接紧密、有意义的整体,进而组成一个生动的场景。

与乐高一样,Intel新一代封装技术的要义也并非单纯的“封装”,而是要在封装内部实现Die与Die之间的全面互联,进而使封装内部的所有Die能够形成一个整体。这是封装技术进化的方向,同时也是Intel先进封装技术攻关的重点。

Intel公司副总裁、封装测试技术开发部门总经理Babak Sabi先生

就像Intel公司副总裁、封装测试技术开发部门总经理Babak Sabi先生在展示现场所说的:我们不仅要将所有的Die封装在一起,更要让他们像一个整体一样工作。

那么下面我们将围绕封装与互联来讨论一系列关键问题。

1、 如何实现封装的水平扩展?

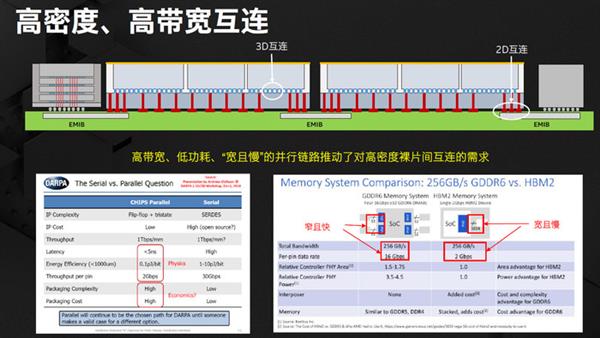

横向扩展的难点在于将不同的高性能Die进行高效互联。所谓高效,意味着这种互联不仅要提供更高带宽、更低延迟,也要同时满足Die的能耗需求。

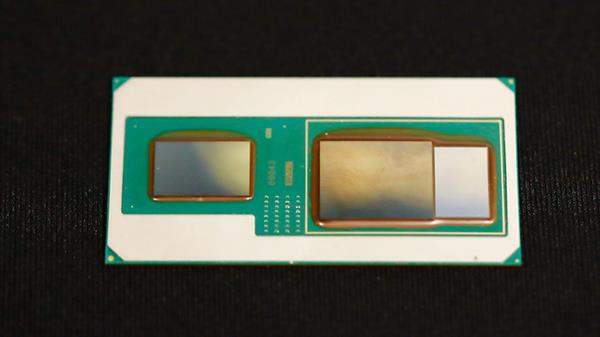

极为难得一见的EMIB半成品,两颗Die中间的部分便是由硅构成的连接部分,只需覆盖一点点就能完成Die之间的数据互联工作,效率很高,很省料

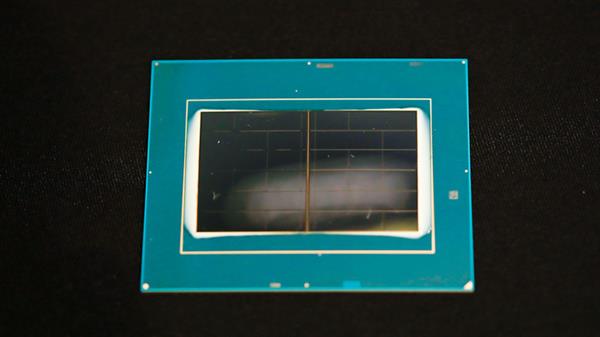

这是一颗相对更完整的工程样品,处在中间位置的两个CPU Die,环绕他们的8颗Die则是HBM内存

基于硅的EMIB在特性上较传统的铜互联有着巨大的优势

Intel的做法是在Die和塑料基板之间预先铺设一层由硅组成的半导体层。这层半导体通过蚀刻技术处理形成线路(并非像制造芯片一样形成晶体管),进而通过金属沉积工序来形成互联电路。

相对于在塑料基板中埋线的传统做法,这种基于硅的工艺能够在更小的空间内铺设更复杂的电路,也就能够实现更多芯片之间更高效的互联。

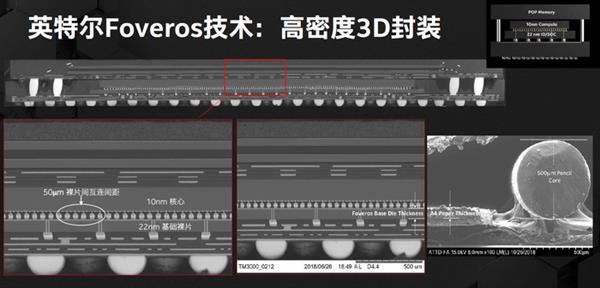

2、 如何实现封装的纵向堆叠?

相对于水平扩展,纵向堆叠要复杂很多,这其中的难点仍旧出在如何解决高效互联问题上。

首先,Die在纵向堆叠之后想要满足各个层之间的互联问题就必须在Die上进行钻孔,并通过金属导线来实现电路的导通。而这种在Die上开孔的行为必须在设计阶段就进行考虑(另一方面,如何在硅这种硬度极高、韧性极差的材质上高效、快速、精确的大量钻孔同样是一件非常困难的事情)。

其次,散热问题非常重要。首要的原则便是发热最高、功耗最大的Die要布置在最上层,这样它离散热器最近,温度也就相对容易控制。当然,功耗高在很多时候就意味着芯片性能高、数据吞吐量大,而这就代表它需要更多的数据和供电针脚直通下层与基板。这会对中下层Die的设计和制造带来更大的挑战。

Intel院士、技术开发部联合总监Ravi Mahajan

用Intel院士、技术开发部联合总监Ravi Mahajan的话解答这一问题会更加简单明了:想要进行纵向堆叠封装,所有参与其中的Die都要想一个单一芯片一样进行整体的设计和考量。

通过右上角的小图我们可以看到多颗Die是如何纵向堆叠在一起的

通过左下角的电子显微镜图,我们可以看到芯片之间的互联以及底层芯片上的垂直开孔

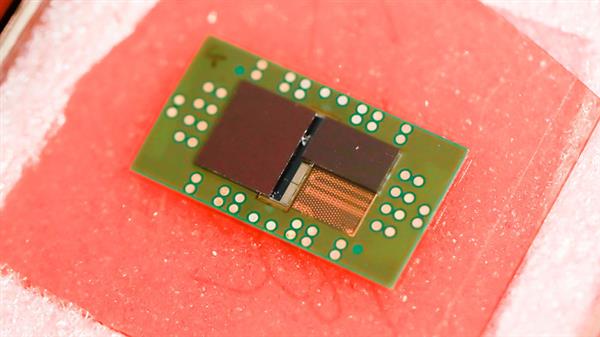

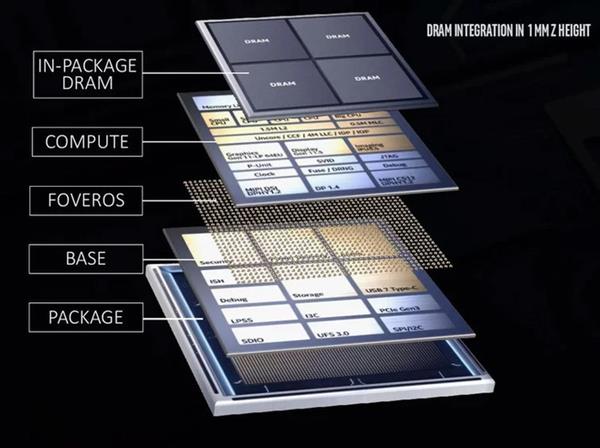

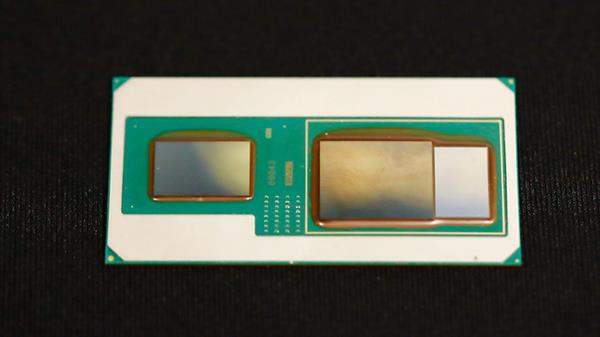

Intel即将发布的Lakefield SoC产品,使用了Foveros技术,将各类功能芯片、CPU和内存完整封装在了一起

现场展示的Lakefield样品,左1为完成品,右2是还没有封装DRAM部分的半成品

3、 先进封装技术在水平和垂直方向上的扩展规模会受到哪些限制?

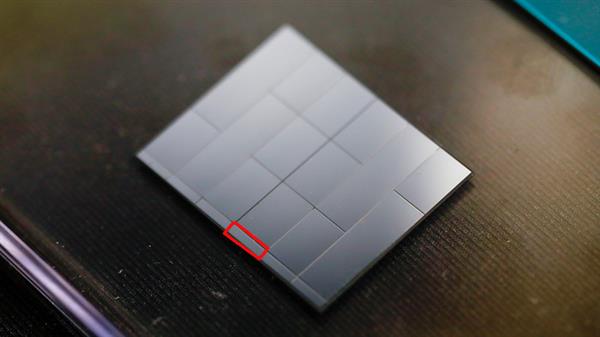

首先,在水平方向上的扩展并不会受到除了成本和总体功耗之因素之外的明显限制,因为EMIB可以在封装内部很好的解决互联问题。在现场,Intel便展示了一颗由28个Die组成的芯片样品,在方寸之间实现了相当壮观的景象。

其次,在垂直方向上的堆叠则会受到功耗、发热、设计等一系列因素的限制。

应用Co-EMIB技术(Co-EMIB=水平互联EMIB+纵向互联Foveros)将14颗Die封装在一起

注意,红框内的部分并不具备任何功能,其存在的意义在于扩大芯片与散热器的接触面积以便提供更高的热交换率(因为硅是热的优秀导体),进而改善散热问题

将两组Die整合在一起,形成一个包含28个功能核心的壮观产品

4、 封装技术的升级很贵吗?

首先,升级工作需要Fab和封测工厂配合进行。

其次,主要的升级工作会集中在封测工厂。

第三,封装技术的升级很贵,但又不像制程工艺的升级那么贵(很抱歉,对于具体的升级成本我们目前仍不知晓)。

第四,升级工作并不需要对现有的工序和流程做出改变,只是会额外的增加工序和设备。

第五,升级工作将首先从Intel美国哈德逊工厂开始。

第六,新技术的实装仍旧需要一段调试和产能爬坡的时期。

5、 我们会在Intel的全新封装技术中看到其他厂商的产品吗?

会的!

还记得前文贴出的这枚芯片么,Intel和AMD终于走在了一起

这是由系统制造商(笔记本厂商)下单完成的量产型产品

Intel虽然拥有大量处理器和存储方面的产品,但为了在一个封装内实现更多的功能,其他IP的参与必不可少。

在现场的展示中我们便能看到Intel将自家的产品与现代的多颗HBM封装在一起。

未来,在新的封装技术实装之后,其他厂商也可以通过购买Intel代工服务的方式来实现多样化的封装。

摩尔定律的一次全新实践

在最初版“摩尔定律”中,集成电路中所容纳的晶体管数量每隔约2年便会提升一倍(我们所熟知的“性能每18个月提升一倍”的说法是由后来的Intel CEO大卫·豪斯在之后提出的)。

但从实际的半导体技术角度出发,我们也必须承认:制程工艺发展速度的放缓在很大程度上影响了摩尔定律的继续实践。作为这一行业标准的提出者,Intel显然有极大的动力继续维护摩尔定律的实践。

而当制程工艺无法满足需求时,另寻他路就成为了必然的选择。

英特尔先进封装技术进化所带来的芯片水平扩展和垂直堆叠能够在很大程度上降低半导体产品的设计和制造难度,带来晶体管密度和芯片整体性能的双提升;因此,无论从哪个层面来看,封装技术在很大程度上都能够成为推动摩尔定律继续向前发展的第二只轮子。

这就相当于是为包括Intel在内的整个半导体行业开辟了全新的发展路径和空间。

在Foveros、EMIB和Co-EMIB的启发下,或许在未来,我们能够像关注制程工艺一样关注封装技术。